CMOS集成電路設計中邏輯門電路分析

在現代數字集成電路(IC)設計中,互補金屬氧化物半導體(CMOS)技術因其低功耗、高噪聲容限和優異的可擴展性而占據主導地位。邏輯門電路作為數字系統的基石,其性能、面積和功耗直接決定了整個芯片的效能。因此,對CMOS邏輯門電路進行深入分析是集成電路設計的核心環節。

一、CMOS邏輯門的基本結構與工作原理

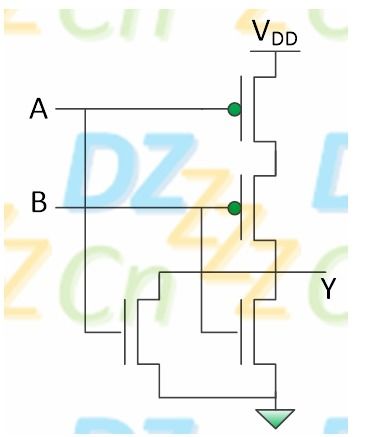

CMOS邏輯門的基本結構由一對互補的MOSFET(金屬氧化物半導體場效應晶體管)構成:P型MOSFET(PMOS)和N型MOSFET(NMOS)。PMOS管作為上拉網絡(PUN),負責在輸出邏輯“1”時連接電源(VDD);NMOS管作為下拉網絡(PDN),負責在輸出邏輯“0”時連接地(GND)。這種互補結構確保了在穩態下,從電源到地的直接通路被阻斷,從而實現了極低的靜態功耗。

以最基本的CMOS反相器(非門)為例:一個PMOS管和一個NMOS管串聯,柵極相連作為輸入端,漏極相連作為輸出端。當輸入為低電平時,PMOS導通,NMOS截止,輸出被上拉至高電平;當輸入為高電平時,PMOS截止,NMOS導通,輸出被下拉至低電平。其他復雜邏輯門(如與非門、或非門)則是通過將多個PMOS和NMOS管以特定方式組合,分別構成上拉和下拉網絡來實現的。

二、關鍵性能參數分析

在集成電路設計中,對邏輯門電路的性能分析主要圍繞以下幾個關鍵參數展開:

- 延遲時間:信號從輸入變化到輸出穩定所需的時間,主要包括上升時間(Tr)和下降時間(Tf)。延遲受晶體管的尺寸(寬長比)、負載電容、互連線電容以及輸入信號邊沿速率的影響。通過優化晶體管尺寸和布局,可以平衡速度與功耗。

- 功耗:

- 靜態功耗:在穩定狀態下,CMOS邏輯門由于沒有直流通路,理論上靜態功耗近乎為零,但實際上存在亞閾值漏電流和柵極漏電流。

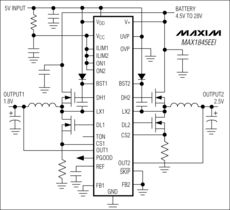

- 動態功耗:主要由電路開關過程中的電容充放電(P = α C VDD2 * f)和短路電流(在輸入信號跳變期間,PMOS和NMOS短暫同時導通)產生。降低電源電壓(VDD)是減少動態功耗最有效的方法之一。

- 噪聲容限:指電路在存在噪聲干擾時仍能正確識別邏輯電平的能力。它由電壓傳輸特性(VTC)曲線決定,通常用高電平噪聲容限(NMH)和低電平噪聲容限(NML)來量化。穩健的設計需要足夠的噪聲容限以應對工藝偏差和環境變化。

- 扇入與扇出:扇入指一個邏輯門的輸入端口數量;扇出指一個邏輯門能夠驅動的同類門數量。扇出過大(重負載)會顯著增加延遲,設計中需要進行緩沖或調整驅動能力。

三、設計考量與優化技術

- 晶體管尺寸縮放:根據邏輯功能,合理設置PMOS與NMOS的寬長比。通常,為了獲得對稱的上升/下降時間,PMOS管的寬度需要設計為NMOS管的2到3倍(因為空穴遷移率低于電子遷移率)。

- 邏輯努力理論:一種系統化的延遲建模與優化方法,通過將路徑延遲分解為邏輯努力、電氣努力和分支努力,幫助設計者快速估算和優化多級邏輯鏈的性能,找到最佳的級數和晶體管尺寸。

- 功耗-性能-面積(PPA)權衡:這是集成電路設計的永恒主題。提高速度往往需要更大的晶體管(增加面積和功耗),而降低功耗又可能犧牲性能。設計者需根據應用場景(如高性能計算、移動設備)確定優化優先級。

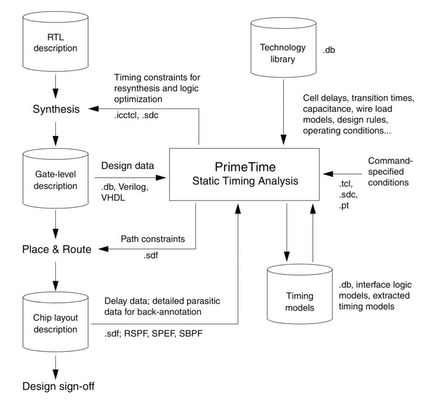

- 工藝角與變異分析:在實際制造中,工藝參數(如晶體管閾值電壓、溝道長度)會在一定范圍內波動。設計必須通過仿真覆蓋典型(TT)、快(FF)、慢(SS)等多個工藝角,以及考慮電壓、溫度(PVT)變化,確保電路在所有條件下都能可靠工作。

四、先進CMOS邏輯結構

隨著工藝節點不斷微縮,傳統CMOS結構面臨挑戰,衍生出一些變體:

- 傳輸門邏輯:利用PMOS和NMOS并聯構成近乎理想的開關,用于構建多路選擇器、鎖存器等。

- 動態邏輯:通過預充電和求值兩個階段工作,減少了實現復雜邏輯所需的晶體管數量,速度更快,但存在電荷泄漏和噪聲敏感等問題。

- 多米諾邏輯:動態邏輯與靜態反相器的結合,兼具高速和驅動能力強的優點,廣泛用于高性能數據路徑中。

###

對CMOS邏輯門電路的深入分析是成功進行集成電路設計的基礎。從基本原理出發,精確建模其延遲、功耗和噪聲特性,并運用邏輯努力等優化方法,設計者能夠在功耗、性能和面積之間取得最佳平衡。隨著技術發展,新的器件結構和設計方法論不斷涌現,但掌握這些核心分析技能,依然是應對未來更復雜、更先進芯片設計挑戰的關鍵。

如若轉載,請注明出處:http://m.wopou.cn/product/44.html

更新時間:2026-04-10 00:07:44